Difference between revisions of "Datel Action Replay PC"

| (5 intermediate revisions by the same user not shown) | |||

| Line 10: | Line 10: | ||

!Pins |

!Pins |

||

!Info |

!Info |

||

!Notes |

|||

|- |

|- |

||

|U1 |

|U1 |

||

| Line 17: | Line 18: | ||

|32 |

|32 |

||

|[http://pdf.datasheetcatalog.com/datasheet/nationalsemiconductor/DS010798.PDF datasheet] |

|[http://pdf.datasheetcatalog.com/datasheet/nationalsemiconductor/DS010798.PDF datasheet] |

||

| |

|||

|- |

|- |

||

|U2 |

|U2 |

||

| Line 24: | Line 26: | ||

|14 |

|14 |

||

|[https://www.onsemi.com/pub/Collateral/MC74HC74A-D.PDF datasheet] |

|[https://www.onsemi.com/pub/Collateral/MC74HC74A-D.PDF datasheet] |

||

| |

|||

|- |

|- |

||

|U3 |

|U3 |

||

|SRAM (8KB) |

|SRAM (8KB) |

||

|Hyundai |

|Hyundai |

||

|HM6264ALJ-10 |

|||

|HM6264 |

|||

|28 |

|28 |

||

|[http://www.protronix.co.za/images/info/HM6264.pdf datasheet] |

|[http://www.protronix.co.za/images/info/HM6264.pdf datasheet] |

||

|8 Kilobytes (8K words by 8-bits), 10 nanoseconds |

|||

|- |

|- |

||

|U4 |

|U4 |

||

|SRAM (128KB) |

|SRAM (128KB) |

||

|Hitachi |

|Hitachi |

||

|HM628128LFP |

|HM628128LFP-7 |

||

|32 |

|32 |

||

|[https://www.digchip.com/datasheets/parts/datasheet/740/HM628128-pdf.php datasheet] |

|[https://www.digchip.com/datasheets/parts/datasheet/740/HM628128-pdf.php datasheet] |

||

|128 Kilobytes (8K words by 8-bits), 70 nanoseconds. |

|||

L=low standby power (10 uW) |

|||

|- |

|- |

||

|U5 |

|U5 |

||

| Line 45: | Line 51: | ||

|8 |

|8 |

||

|[http://www.ti.com/lit/ds/symlink/ne555.pdf datasheet] |

|[http://www.ti.com/lit/ds/symlink/ne555.pdf datasheet] |

||

| |

|||

|- |

|- |

||

|P1 |

|P1 |

||

| Line 52: | Line 59: | ||

|24 |

|24 |

||

|[https://www.latticesemi.com/-/media/LatticeSemi/Documents/DataSheets/PAL/PALCE20V8DataSheet.ashx?la=en datasheet] |

|[https://www.latticesemi.com/-/media/LatticeSemi/Documents/DataSheets/PAL/PALCE20V8DataSheet.ashx?la=en datasheet] |

||

| rowspan="4" |The part number "PALCE20V8Q" decodes as: |

|||

20 inputs, 8 flip/flops or outputs, Quarter power (55 mA Icc) |

|||

|- |

|- |

||

|P2 |

|P2 |

||

| Line 76: | Line 85: | ||

|C1 |

|C1 |

||

|Capacitor |

|Capacitor |

||

| |

|||

| |

| |

||

| |

| |

||

| Line 83: | Line 93: | ||

|C2 |

|C2 |

||

|Capacitor |

|Capacitor |

||

| |

|||

| |

| |

||

| |

| |

||

| Line 91: | Line 102: | ||

|Capacitor |

|Capacitor |

||

| |

| |

||

|1 uF / 63v |

|||

| |

| |

||

| |

| |

||

| Line 97: | Line 109: | ||

|D1 |

|D1 |

||

|Diode |

|Diode |

||

| |

|||

| |

| |

||

| |

| |

||

| Line 104: | Line 117: | ||

|D2 |

|D2 |

||

|Diode |

|Diode |

||

| |

|||

| |

| |

||

| |

| |

||

| Line 112: | Line 126: | ||

|Resistor |

|Resistor |

||

| |

| |

||

|23k Ω |

|||

| |

| |

||

| |

| |

||

| Line 119: | Line 134: | ||

|Resistor |

|Resistor |

||

| |

| |

||

|100k Ω |

|||

| |

| |

||

| |

| |

||

| Line 127: | Line 143: | ||

| |

| |

||

|1K Ω |

|1K Ω |

||

| |

|||

| |

| |

||

| |

| |

||

| Line 134: | Line 151: | ||

| |

| |

||

|DB-9 male |

|DB-9 male |

||

| |

|||

| |

| |

||

| |

| |

||

| Line 139: | Line 157: | ||

<br /> |

<br /> |

||

=== |

===Dip Switches / Jumpers:=== |

||

The right 3 switches on the dip switch block (S4-S6) control the ROM address, while the left two switches control the IO port. S3, the third switch from the left, is not explained. |

|||

The 6 jumper pins at JP1-6 are used to set the IRQ. A vertical pin closing the top and bottom contact selects that IRQ |

|||

The manual lists the following values: |

|||

{| class="wikitable" |

|||

|+ROM Address |

|||

!S4 |

|||

!S5 |

|||

!S6 |

|||

!Address |

|||

|- |

|||

|UP |

|||

|UP |

|||

|UP |

|||

|DC00h |

|||

|- |

|||

|UP |

|||

|DOWN |

|||

|DOWN |

|||

|D800h |

|||

|- |

|||

|DOWN |

|||

|UP |

|||

|DOWN |

|||

|D400h |

|||

|- |

|||

|DOWN |

|||

|UP |

|||

|UP |

|||

|D200h |

|||

|- |

|||

|UP |

|||

|UP |

|||

|DOWN |

|||

|D000h |

|||

|- |

|||

|DOWN |

|||

|DOWN |

|||

|UP |

|||

|CC00h |

|||

|- |

|||

|UP |

|||

|DOWN |

|||

|UP |

|||

|C800h |

|||

|- |

|||

|DOWN |

|||

|DOWN |

|||

|DOWN |

|||

|Unspecified (TODO: test) |

|||

|} |

|||

<br /> |

|||

{| class="wikitable" |

|||

|+IO Port |

|||

!S1 |

|||

!S2 |

|||

!Port |

|||

|- |

|||

|UP |

|||

|UP |

|||

|280h |

|||

|- |

|||

|DOWN |

|||

|UP |

|||

|290h |

|||

|- |

|||

|UP |

|||

|DOWN |

|||

|2A0h |

|||

|- |

|||

|DOWN |

|||

|DOWN |

|||

|2B0h |

|||

|}<br /> |

|||

{| class="wikitable" |

|||

|+IRQ |

|||

!JP1 |

|||

!JP2 |

|||

!JP3 |

|||

!JP4 |

|||

!JP5 |

|||

!JP6 |

|||

|- |

|||

|2 |

|||

|3 |

|||

|4 |

|||

|5 |

|||

|6 |

|||

|7 |

|||

|} |

|||

===Firmware=== |

|||

[https://archive.org/details/actionreplaypcfirmwarev4 The firmware] is 128 kilobytes, separated into 16 8KB Pages. |

[https://archive.org/details/actionreplaypcfirmwarev4 The firmware] is 128 kilobytes, separated into 16 8KB Pages. |

||

Each page begins with a header that says which page it is, and mentions "(c) 1993 DATEL" |

Each page begins with a header that says which page it is, and mentions "(c) 1993 DATEL" |

||

| Line 145: | Line 256: | ||

The AREPLAY.COM file has error strings for "Action Replay ram not switchable" and "Replay base address is not being shadowed" which suggests the larger SRAM chip (U4) is being used to shadow the EPROM at runtime. |

The AREPLAY.COM file has error strings for "Action Replay ram not switchable" and "Replay base address is not being shadowed" which suggests the larger SRAM chip (U4) is being used to shadow the EPROM at runtime. |

||

There was at least one upgrade to the EPROM provided, which involved mailing out a replacement chip to users. |

There was at least one upgrade to the EPROM provided, which involved mailing out a replacement chip to users. |

||

<br /> |

<br /> |

||

=== |

===Anti-virus functionality=== |

||

The firmware contains [https://twitter.com/Foone/status/1232324301656735745 the signature of 50 viruses], starting at offset 0x164D8. |

The firmware contains [https://twitter.com/Foone/status/1232324301656735745 the signature of 50 viruses], starting at offset 0x164D8. |

||

| Line 202: | Line 313: | ||

|Orange |

|Orange |

||

|} |

|} |

||

===Credits:=== |

|||

The firmware contains credits at offset 4F64: (TODO: See if you can view this from within the program) |

|||

Action Replay v1.3 (c) 1993 DATEL |

|||

Programmer ............................ Simon P.Constable |

|||

Project Manager ......................... Wayne H.Beckett |

|||

Design ................................... Mike J.Connors |

|||

......................................... Wayne H.Beckett |

|||

Hardware .................................. Roy C.Harding |

|||

Support .................................... Mark Wallace |

|||

.......................................... Damon P.Barwin |

|||

===Twitter Threads:=== |

===Twitter Threads:=== |

||

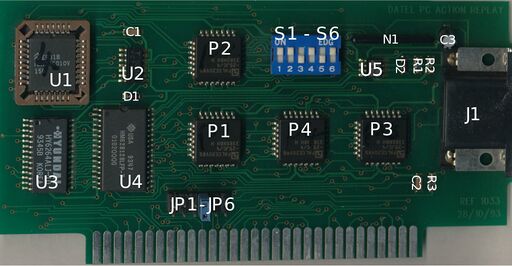

Latest revision as of 21:24, 6 March 2020

PCB components:

| Name | Type | Manufacturer | Name/Value | Pins | Info | Notes |

|---|---|---|---|---|---|---|

| U1 | EPROM | National Semiconductor | NM27C010 | 32 | datasheet | |

| U2 | Dual Flip-flop | HC74A | 14 | datasheet | ||

| U3 | SRAM (8KB) | Hyundai | HM6264ALJ-10 | 28 | datasheet | 8 Kilobytes (8K words by 8-bits), 10 nanoseconds |

| U4 | SRAM (128KB) | Hitachi | HM628128LFP-7 | 32 | datasheet | 128 Kilobytes (8K words by 8-bits), 70 nanoseconds.

L=low standby power (10 uW) |

| U5 | 555 Timer | STMicroelectronics | NE555 | 8 | datasheet | |

| P1 | Programmable Logic Array | AMD | PALCE20V8Q | 24 | datasheet | The part number "PALCE20V8Q" decodes as:

20 inputs, 8 flip/flops or outputs, Quarter power (55 mA Icc) |

| P2 | Programmable Logic Array | AMD | PALCE20V8Q | 24 | datasheet | |

| P3 | Programmable Logic Array | AMD | PALCE20V8Q | 24 | datasheet | |

| P4 | Programmable Logic Array | AMD | PALCE20V8Q | 24 | datasheet | |

| C1 | Capacitor | |||||

| C2 | Capacitor | |||||

| C3 | Capacitor | 1 uF / 63v | ||||

| D1 | Diode | |||||

| D2 | Diode | |||||

| R1 | Resistor | 23k Ω | ||||

| R2 | Resistor | 100k Ω | ||||

| R3 | Resistor | 1K Ω | ||||

| J1 | Connector | DB-9 male |

Dip Switches / Jumpers:

The right 3 switches on the dip switch block (S4-S6) control the ROM address, while the left two switches control the IO port. S3, the third switch from the left, is not explained.

The 6 jumper pins at JP1-6 are used to set the IRQ. A vertical pin closing the top and bottom contact selects that IRQ

The manual lists the following values:

| S4 | S5 | S6 | Address |

|---|---|---|---|

| UP | UP | UP | DC00h |

| UP | DOWN | DOWN | D800h |

| DOWN | UP | DOWN | D400h |

| DOWN | UP | UP | D200h |

| UP | UP | DOWN | D000h |

| DOWN | DOWN | UP | CC00h |

| UP | DOWN | UP | C800h |

| DOWN | DOWN | DOWN | Unspecified (TODO: test) |

| S1 | S2 | Port |

|---|---|---|

| UP | UP | 280h |

| DOWN | UP | 290h |

| UP | DOWN | 2A0h |

| DOWN | DOWN | 2B0h |

| JP1 | JP2 | JP3 | JP4 | JP5 | JP6 |

|---|---|---|---|---|---|

| 2 | 3 | 4 | 5 | 6 | 7 |

Firmware

The firmware is 128 kilobytes, separated into 16 8KB Pages. Each page begins with a header that says which page it is, and mentions "(c) 1993 DATEL"

The AREPLAY.COM file has error strings for "Action Replay ram not switchable" and "Replay base address is not being shadowed" which suggests the larger SRAM chip (U4) is being used to shadow the EPROM at runtime.

There was at least one upgrade to the EPROM provided, which involved mailing out a replacement chip to users.

Anti-virus functionality

The firmware contains the signature of 50 viruses, starting at offset 0x164D8.

Each name is proceeded by an 0xFE character, can be up to 26 letters long, and is padded with spaces.

IBM Control

The external "paddle" features a button, switch, and LED. The PCB inside calls it the "Datel IBM Control"

| Connection | Color | |

|---|---|---|

| 1 | N/C | N/A |

| 2 | LED | Brown |

| 3 | Switch | Black |

| 4 | Button | Blue |

| 5 | Ground | Green |

| 6 | N/C | |

| 7 | N/C | Yellow |

| 8 | N/C | |

| 9 | N/C | |

| Shell | N/C | Orange |

Credits:

The firmware contains credits at offset 4F64: (TODO: See if you can view this from within the program)

Action Replay v1.3 (c) 1993 DATEL Programmer ............................ Simon P.Constable Project Manager ......................... Wayne H.Beckett Design ................................... Mike J.Connors ......................................... Wayne H.Beckett Hardware .................................. Roy C.Harding Support .................................... Mark Wallace .......................................... Damon P.Barwin

Twitter Threads:

- When the Brandon unit first showed up on ebay (April 24th, 2019)

- In response to the LGR video (February 21st, 2020)

- Firmware image reverse engineering (February 25th 2020)

- Status update after the card arrived (February 27th, 2020)

Related Links:

- Lazy Game Reviews video on the Action Replay PC

- Manual, PCB images, and software

- VCFed thread

- Version 4 firmware dump